IC載板 趨勢演進

IC載板 趨勢演進

![]() 隨晶圓製程技術演進,相對使晶圓佈線密度、傳輸速率及訊號干擾等效能需求提高,而打線載板受板邊金線接點密度無法突破之限制,故在覆晶封裝挾微植球之優勢,成為未來載板發展主流。

隨晶圓製程技術演進,相對使晶圓佈線密度、傳輸速率及訊號干擾等效能需求提高,而打線載板受板邊金線接點密度無法突破之限制,故在覆晶封裝挾微植球之優勢,成為未來載板發展主流。

![]() 順應未來電子產品朝輕薄短小、高效能與低功耗為設計趨勢,覆晶載板之晶片封裝方式將由現階段單晶片封裝型態演變至多晶片與整合型晶片封裝。

順應未來電子產品朝輕薄短小、高效能與低功耗為設計趨勢,覆晶載板之晶片封裝方式將由現階段單晶片封裝型態演變至多晶片與整合型晶片封裝。

![]() 隨著技術發展的趨勢在於「厚度空間」的研發,傳統以Wirebond方式連接晶片,逐漸轉向Flip Chip封裝方式,設計朝向薄板/細線路/微凸塊間距發展。

隨著技術發展的趨勢在於「厚度空間」的研發,傳統以Wirebond方式連接晶片,逐漸轉向Flip Chip封裝方式,設計朝向薄板/細線路/微凸塊間距發展。

![]() 隨著晶片處理速度與日俱增與高I/O的需求,覆晶基板將朝向細線距凸塊組裝,BOT設計會是其中選擇之一,藉此達到UBM電鍍銅凸塊組裝。另一方面,三維組裝技術對於基板之高密度凸塊及高剛性之需求亦為下世代基板發展方向。

隨著晶片處理速度與日俱增與高I/O的需求,覆晶基板將朝向細線距凸塊組裝,BOT設計會是其中選擇之一,藉此達到UBM電鍍銅凸塊組裝。另一方面,三維組裝技術對於基板之高密度凸塊及高剛性之需求亦為下世代基板發展方向。

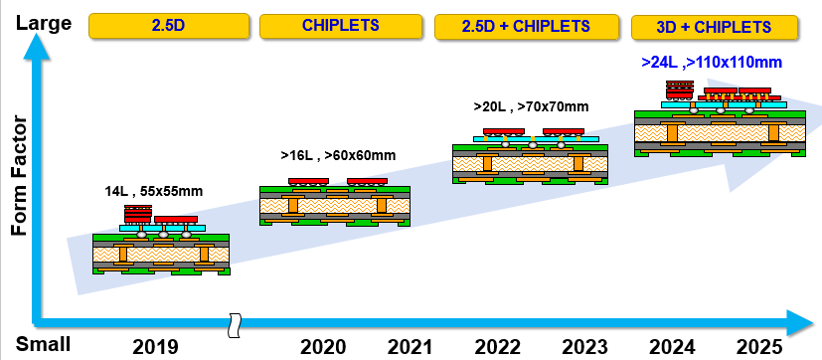

![]() 持續開發高層板(>22L),大尺寸基板(>100mmSQ)與內埋元件基板,以符合客戶5G相關產品及人工智慧(AI)及HPC(High Performance Computing)應用。

持續開發高層板(>22L),大尺寸基板(>100mmSQ)與內埋元件基板,以符合客戶5G相關產品及人工智慧(AI)及HPC(High Performance Computing)應用。